Er was een tijdperk waarin computers zo gigantisch groot waren dat om ze te installeren gemakkelijk een kamerruimte nodig was. Maar tegenwoordig zijn ze zo geëvolueerd dat we ze zelfs gemakkelijk als notebooks kunnen dragen. De innovatie die dit mogelijk maakte, was het concept van Integrated Circuits. In Geïntegreerde schakelingen , een groot aantal actieve en passieve elementen samen met hun onderlinge verbindingen worden ontwikkeld over een kleine siliciumwafel, typisch met een doorsnede van 50 bij 50 mils. De basisprocessen die worden gevolgd voor de productie van dergelijke circuits omvatten epitaxiale groei, gemaskeerde diffusie van onzuiverheden, oxidegroei en oxide-etsing, waarbij fotolithografie wordt gebruikt voor het maken van een patroon.

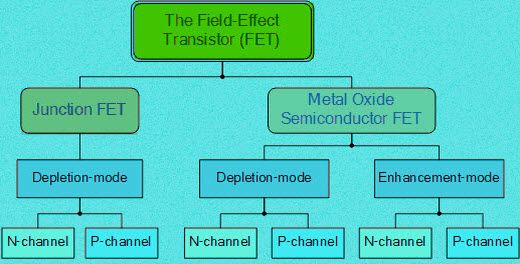

De componenten over de wafer zijn onder meer weerstanden, transistors, diodes, condensatoren enz. Het meest gecompliceerde element om over IC's te vervaardigen zijn transistors. Transistors zijn van verschillende typen zoals CMOS, BJT, FET. We kiezen het type transistortechnologie dat via een IC wordt geïmplementeerd op basis van de vereisten. Laten we in dit artikel vertrouwd raken met het concept van CMOS-fabricage (of) fabricage van transistors als CMOS.

CMOS-fabricage

Voor minder energieverlies CMOS-technologie wordt gebruikt voor het implementeren van transistors. Als we een sneller circuit nodig hebben, worden transistors geïmplementeerd IC gebruiken BJT Fabricage van CMOS-transistors aangezien IC's op drie verschillende manieren kunnen worden gedaan.

De N-well / P-well-technologie, waarbij n-type diffusie wordt uitgevoerd over een p-type substraat of p-type diffusie wordt uitgevoerd over respectievelijk n-type substraat.

De Twin Well-technologie , waar NMOS en PMOS-transistor worden ontwikkeld over de wafel door gelijktijdige diffusie over een epitaxiale groeibasis, in plaats van een substraat.

Het silicon On Insulator-proces, waarbij in plaats van silicium als substraat te gebruiken, een isolatiemateriaal wordt gebruikt om de snelheid en de gevoeligheid voor vergrendeling te verbeteren.

N-well / P-well-technologie

CMOS kan worden verkregen door beide te integreren NMOS- en PMOS-transistors over dezelfde siliciumwafel. In N-well-technologie wordt een n-type put gediffundeerd op een p-type substraat, terwijl dit in P-well omgekeerd is.

CMOS-fabricagestappen

De CMOS-fabricageproces stromen wordt uitgevoerd met behulp van twintig basis fabricagestappen terwijl vervaardigd met behulp van N-well / P-well-technologie.

Maken van CMOS met N goed

Stap 1: Eerst kiezen we een substraat als basis voor fabricage. Voor N-well wordt een P-type siliciumsubstraat geselecteerd.

Substraat

Stap 2 - Oxidatie: De selectieve diffusie van onzuiverheden van het n-type wordt bereikt door Si02 als een barrière te gebruiken die delen van de wafel beschermt tegen vervuiling van het substraat. SiOtweewordt aangelegd door een oxidatieproces waarbij het substraat wordt blootgesteld aan hoogwaardige zuurstof en waterstof in een oxidatiekamer van ongeveer 10000c

Oxidatie

Stap 3 - Teelt van fotoresist: Om het selectief etsen mogelijk te maken, wordt de Si02-laag in dit stadium aan het fotolithografisch proces onderworpen. Bij dit proces wordt de wafel bedekt met een uniforme film van een fotogevoelige emulsie.

Teelt van fotoresist

Stap 4 - Maskeren: Deze stap is de voortzetting van het fotolithografieproces. In deze stap wordt met behulp van een sjabloon een gewenst patroon van openheid gemaakt. Dit sjabloon wordt gebruikt als een masker over de fotolak. Het substraat wordt nu blootgesteld aan UV straling de fotoresist die aanwezig is onder de blootgestelde gebieden van het masker wordt gepolymeriseerd.

Maskeren van fotoresist

Stap 5 - Verwijderen van onbelichte fotoresist: Het masker wordt verwijderd en het onbelichte gebied van de fotolak wordt opgelost door een wafel te ontwikkelen met een chemische stof zoals trichloorethyleen.

Verwijdering van fotoresist

Stap 6 - Ets: De wafel wordt ondergedompeld in een etsoplossing van fluorwaterstofzuur, die het oxide verwijdert uit de gebieden waardoor doteermiddelen moeten worden verspreid.

Etsen van SiO2

Stap 7 - Verwijdering van de hele fotolaklaag: Tijdens de etsproces worden die delen van Si02 die worden beschermd door de fotolaklaag niet beïnvloed. Het fotolakmasker wordt nu verwijderd met een chemisch oplosmiddel (hete H2SO4).

Verwijdering van fotolaklaag

Stap 8 - Vorming van N-well: De n-type onzuiverheden worden in het p-type substraat gediffundeerd door het blootgestelde gebied en vormen zo een N-putje.

Vorming van N-well

Stap 9 - Verwijderen van SiO2: De laag SiO2 wordt nu verwijderd door fluorwaterstofzuur te gebruiken.

Verwijdering van SiO2

Stap 10 - Afzetting van polysilicium: De verkeerde uitlijning van de poort van a CMOS-transistor zou leiden tot de ongewenste capaciteit die het circuit zou kunnen beschadigen. Om dit 'zelf-uitgelijnde poortproces' te voorkomen heeft dus de voorkeur waar poortgebieden worden gevormd vóór de vorming van bron en afvoer met behulp van ionenimplantatie.

Afzetting van polysilicium

Polysilicium wordt gebruikt voor de vorming van de poort omdat het bestand is tegen hoge temperaturen van meer dan 80000c wanneer een wafel wordt onderworpen aan gloeimethoden voor de vorming van source en drain. Polysilicium wordt afgezet door te gebruiken Chemisch afzettingsproces over een dunne laag gate-oxide. Dit dunne poortoxide onder de polysiliciumlaag voorkomt verdere dotering onder het poortgebied.

Stap 11 - Vorming van poortregio: Behalve de twee regio's die nodig zijn voor de vorming van de poort voor NMOS- en PMOS-transistors het resterende deel van polysilicium wordt verwijderd.

Vorming van Gate Region

Stap 12 - Oxidatieproces: Een oxidatielaag wordt over de wafel afgezet die als een verdere bescherming fungeert diffusie- en metallisatieprocessen

Oxidatieproces

Stap 13 - Maskering en diffusie: Voor het maken van gebieden voor diffusie van n-type onzuiverheden met behulp van een maskeerproces worden kleine openingen gemaakt.

Maskeren

Met behulp van diffusieproces worden drie n + regio's ontwikkeld voor de vorming van terminals van NMOS.

N-diffusie

Stap 14 - Verwijdering van oxide: De oxidelaag wordt verwijderd.

Verwijdering van oxide

Stap 15 - P-type diffusie: Vergelijkbaar met de n-type diffusie voor het vormen van de terminals van PMOS worden p-type diffusie uitgevoerd.

P-type diffusie

Stap 16 - Aanbrengen van dikveldoxide: Voordat de metalen aansluitingen worden gevormd, wordt een oxide met een dik veld aangelegd om een beschermende laag te vormen voor de gebieden van de wafer waar geen aansluitingen nodig zijn.

Dikke veldoxidelaag

Stap 17 - Metallisatie: Deze stap wordt gebruikt voor de vorming van metalen terminals die onderlinge verbindingen kunnen bieden. Aluminium wordt over de hele wafel uitgesmeerd.

Metallisatie

Stap 18 - Verwijderen van overtollig metaal: Het overtollige metaal wordt van de wafel verwijderd.

Stap 19 - Vorming van terminals: In de spleten die zijn gevormd na het verwijderen van overtollige metalen zijn klemmen gevormd voor de verbindingen.

Vorming van terminals

Stap 20 - De terminalnamen toewijzen: Er worden namen toegekend aan de terminals van NMOS- en PMOS-transistors

Terminal-namen toewijzen

Maken van CMOS met behulp van P well-technologie

Het p-well-proces is vergelijkbaar met het N-well-proces, behalve dat hier een n-type substraat wordt gebruikt en p-type diffusies worden uitgevoerd. Omwille van de eenvoud heeft gewoonlijk de N-put-werkwijze de voorkeur.

Twin Tube Fabrication van CMOS

Met behulp van het Twin-tube-proces kan de versterking van P- en N-type apparaten worden geregeld. Verschillende stappen betrokken bij het fabricage van CMOS met behulp van de Twin-tube-methode zijn als volgt

- Er wordt een licht gedoteerd n- of p-type substraat genomen en de epitaxiale laag wordt gebruikt. Epitaxiale laag beschermt het latch-up probleem in de chip.

- De siliciumlagen van hoge zuiverheid met gemeten dikte en exacte doteerstofconcentratie worden gekweekt.

- Vorming van buizen voor P- en N-put.

- Dunne oxide constructie voor bescherming tegen vervuiling tijdens diffusieprocessen.

- Source en drain worden gevormd met behulp van ionenimplantatiemethoden.

- Uitsnijdingen zijn gemaakt om delen voor metalen contacten te maken.

- Metallisatie wordt gedaan voor het tekenen van metalen contacten

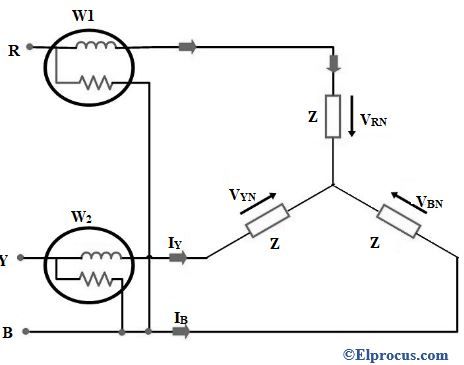

CMOS IC-indeling

Het bovenaanzicht van naar CMOS fabricage en lay-out is gegeven. Hier zijn verschillende metalen contacten en N-putdiffusies duidelijk te zien.

CMOS IC-indeling

Dit gaat dus allemaal over CMOS-fabricagetechnieken Laten we eens kijken naar een 1-in-square wafel verdeeld in 400 chips met een oppervlak van 50 mil bij 50 mils. Er is een oppervlakte van 50 mil2 nodig om een transistor te fabriceren. Daarom bevat elk IC 2 transistors, dus er zijn 2 x 400 = 800 transistors op elke wafer gebouwd. Als er per batch 10 wafers worden verwerkt, kunnen 8000 transistors tegelijkertijd worden vervaardigd. Wat zijn verschillende componenten die u op een IC hebt waargenomen?