De krachtigste en belangrijkste functies zijn interrupts in 8051 microcontroller In de meeste real-time processen moet de eigenlijke taak enige tijd worden stopgezet om bepaalde omstandigheden goed te kunnen afhandelen - het vereist actie - en vervolgens terugkeren naar de hoofdtaak. Voor het uitvoeren van dergelijke programma's zijn interrupts nodig. Het verschilt volledig van de polling-methode waarbij de processor elk apparaat achtereenvolgens moet controleren en moet vragen of de service vereist is of niet, terwijl hij meer processortijd verbruikt.

Onderbreekt in 8051 microcontroller

Onderbrekingen in 8051-microcontroller zijn wenselijker om de regelmatige statuscontrole van de gekoppelde apparaten of ingebouwde apparaten te verminderen. Interrupt is een gebeurtenis die het hoofdprogramma tijdelijk onderbreekt, de besturing doorgeeft aan een speciale codesectie, de gebeurtenisgerelateerde functie uitvoert en de hoofdprogrammastroom hervat waar het was gestopt.

Interrupts zijn van verschillende typen, zoals software en hardware, maskeerbaar en niet-maskeerbaar, fixed en vector interrupts, enzovoort. Interrupt Service Routine (ISR) komt in beeld wanneer de interrupt optreedt, en vertelt de processor vervolgens om de juiste actie te ondernemen voor de interrupt, en na ISR-uitvoering springt de controller naar het hoofdprogramma.

Soorten onderbrekingen in 8051 Microcontroller

De 8051-microcontroller kan vijf verschillende gebeurtenissen herkennen die ervoor zorgen dat het hoofdprogramma de normale uitvoering onderbreekt. Deze vijf bronnen van interrupts in 8051 zijn:

- Timer 0 overlooponderbreking- TF0

- Timer 1 overlooponderbreking - TF1

- Externe hardware-onderbreking INT0

- Externe hardware-onderbreking - INT1

- Seriële communicatie-onderbreking - RI / TI

De timer- en seriële interrupts worden intern gegenereerd door de microcontroller, terwijl de externe interrupts worden gegenereerd door extra interfacing-apparaten of schakelaars die extern zijn aangesloten op de microcontroller. Deze externe onderbrekingen kunnen worden getriggerd via rand of niveau. Wanneer een onderbreking optreedt, voert de microcontroller de onderbrekingsserviceroutine uit zodat de geheugenlocatie overeenkomt met de onderbreking die deze inschakelt. De interrupt die overeenkomt met de geheugenlocatie wordt gegeven in de onderstaande interruptvectortabel.

Onderbreek vectortabel

Onderbrekingsstructuur van 8051 Microcontroller

Bij ‘RESET’ worden alle interrupts uitgeschakeld en daarom moeten al deze interrupts worden ingeschakeld door software. In al deze vijf interrupts, als iemand of alle zijn geactiveerd, stelt dit de overeenkomstige interruptvlaggen in zoals weergegeven in de afbeelding. Al deze interrupts kunnen per bit worden ingesteld of gewist in een speciaal functieregister dat Interrupt Enabled (IE) is, en dit hangt weer af van de prioriteit, die wordt uitgevoerd door het IP-interruptprioriteitsregister.

Onderbreek de structuur van de 8051-microcontroller

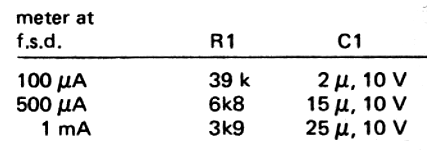

Interrupt Enable (IE) Registreren: Dit register is verantwoordelijk voor het in- en uitschakelen van de onderbreking. Het is een bit-adresseerbaar register waarin EA moet worden ingesteld op één om interrupts mogelijk te maken. De corresponderende bit in dit register maakt bepaalde onderbrekingen mogelijk, zoals timer, externe en seriële ingangen. In het onderstaande IE-register activeert bit dat overeenkomt met 1 de interrupt en 0 schakelt de interrupt uit.

Interrupt Enable (IE) Registreren

Interrupt Priority Register (IP): Het is ook mogelijk om de prioriteitsniveaus van de interrupts te wijzigen door de corresponderende bit in het Interrupt Priority (IP) -register in te stellen of te wissen, zoals weergegeven in de afbeelding. Hierdoor kan de interrupt met lage prioriteit de interrupt met hoge prioriteit onderbreken, maar wordt de onderbreking door een andere interrupt met lage prioriteit verhinderd. Evenzo kan de onderbreking met hoge prioriteit niet worden onderbroken. Als deze interruptprioriteiten niet zijn geprogrammeerd, voert de microcontroller uit op een vooraf gedefinieerde manier en is de volgorde INT0, TF0, INT1, TF1 en SI.

IP-register

TCON Registreren: Naast de bovenstaande twee registers specificeert het TCON-register het type externe interrupt naar de 8051-microcontroller, zoals weergegeven in de afbeelding. De twee externe interrupts, of ze nu flank of niveau geactiveerd zijn, specificeren door dit register door een set of worden gewist door de juiste bits erin. En het is ook een beetje adresseerbaar register.

TCON-register

Onderbreek het programmeren in 8051

1. timer onderbreken programmeren

Timer 0 en timer 1 interrupts worden gegenereerd door de timerregisterbits TF0 en TF1. Deze onderbreekt programmeren door C-code houdt in:

- De timer selecteren door het TMOD-register en de werkingsmodus te configureren.

- De beginwaarden van TLx en THx voor geschikte modi kiezen en laden.

- Het inschakelen van de IE-registers en de bijbehorende timerbit erin.

- De timer-run-bit instellen om de timer te starten.

- Schrijven van de subroutine voor de timer voor de benodigde tijd en wis timerwaarde TRx aan het einde van de subroutine.

Timer onderbreking programmeren

2. externe hardware onderbreking programmeren

8051-microcontrollers bestaan uit twee externe hardware-interrupts: INT0 en INT1 zoals eerder besproken. Deze zijn ingeschakeld op pin 3.2 en pin 3.3. Deze kunnen edge-getriggerd of level-getriggerd zijn. Bij level triggering maakt de low op pin 3.2 de interrupt mogelijk, terwijl op pin 3.2 - de high naar low overgang de flank getriggerde interrupt mogelijk maakt. Deze flank-triggering of niveau-triggering wordt beslist door het TCON-register dat hierboven is besproken. De programmeerprocedure in 8051 is als volgt:

- Schakel het overeenkomstige bit van externe interrupt in IE-register in.

- Als het niveau-triggering is, schrijf dan gewoon de subroutine die geschikt is voor deze interrupt, of schakel anders de TCON-registerbit in die overeenkomt met de door de flank getriggerde interrupt - of het nu INT0 of INT1 is.

Programmering onderbreken van externe hardware

3. programmering van seriële communicatie onderbreken

Onderbrekingen in de seriële communicatie komen in beeld wanneer er gegevens moeten worden verzonden of ontvangen. Aangezien één interruptbit is ingesteld voor zowel TI (Transfer Interrupt) als RI (Receiver Interrupt) vlaggen, moet de Interrupt Service-routine deze vlaggen onderzoeken om de feitelijke interrupt te kennen.

De logische OR-bewerking van deze twee vlaggen (RI en TI) veroorzaakt deze onderbreking en wordt alleen door de software gewist. Hier wordt een speciaal register SCON gebruikt voor de besturing communicatie operatie door de corresponderende bits erin in te schakelen.

- Configureer het IE-register om seriële onderbreking in te schakelen

- Configureer het SCON-register voor ontvangst of overdracht

- Schrijf een subroutine voor deze interrupt met de juiste functie en wis TI- of RI-vlaggen met in deze routine.

Seriële onderbrekingsprogrammering

Dit gaat allemaal over interrupts in 8051-microcontroller, typen, hun structuur en programmering. Ik hoop dat je misschien goede informatie uit dit artikel hebt gekregen. U kunt ons ook schrijven in het onderstaande commentaargedeelte voor de realtime implementatie van microcontroller projecten zodat we u kunnen helpen voor een betere hands-on ervaring.

Fotocredits

- Onderbreekt in 8051 microcontroller door ingenieursgarage

- Onderbreek vectortabel door 8051projecten

- Structuur van 8051 microcontroller onderbreken door borstel

- Interrupt Enable (IE) Registreren door elektronen

- IP registreren door circuit vandaag

- TCON Registreer door circuit vandaag